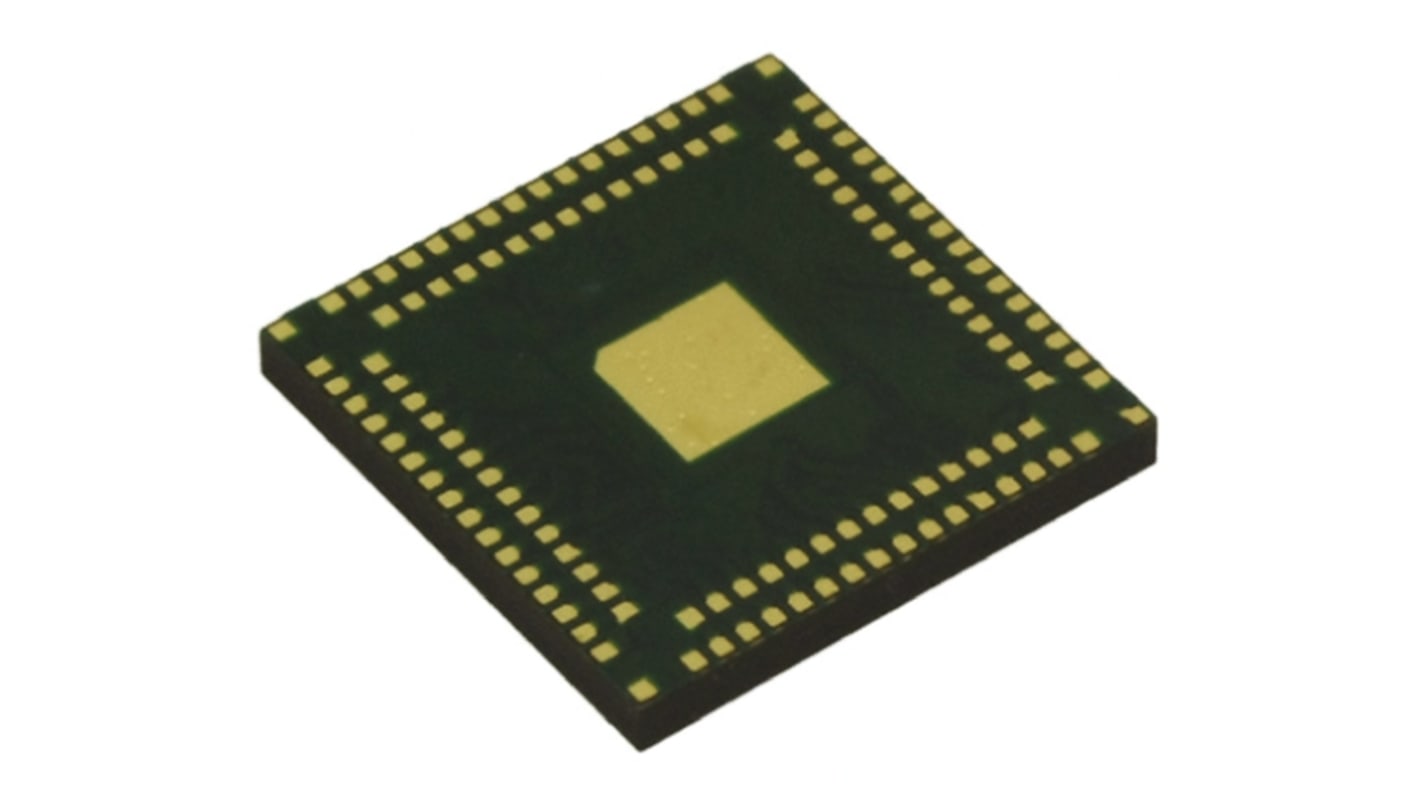

XMOS XS1-L02A-QF124-C5 Multi-Core, XS1 Microcontroller, 60 MHz, 128kB FLASH, 124-Pin QFN

- RS庫存編號:

- 729-9951

- 製造零件編號:

- XS1-L02A-QF124-C5

- 製造商:

- XMOS

此圖片僅供參考,請參閲產品詳細資訊及規格

可享批量折扣

小計(1 件)*

HK$269.60

訂單超過 HK$250.00 免費送貨

暫時缺貨

- 從 2026年8月31日 發貨

**需要更多嗎?**輸入您需要的數量,然後按一下「查看送貨日期」以查詢更多庫存和送貨詳細資訊。

單位 | 每單位 |

|---|---|

| 1 - 41 | HK$269.60 |

| 42 - 83 | HK$263.70 |

| 84 + | HK$258.10 |

* 參考價格

- RS庫存編號:

- 729-9951

- 製造零件編號:

- XS1-L02A-QF124-C5

- 製造商:

- XMOS

規格

產品概覽和技術數據資料表

法例與合規

產品詳細資訊

透過選取一個或多個屬性來查找類似產品。

選取全部 | 屬性 | 值 |

|---|---|---|

| 品牌 | XMOS | |

| Series | XS1 | |

| Product Type | Microcontroller | |

| Package Type | QFN | |

| Mount Type | Surface | |

| Pin Count | 124 | |

| Device Core | Multi-Core | |

| Interface Type | JTAG, SPI | |

| Program Memory Size | 128kB | |

| Maximum Clock Frequency | 60MHz | |

| RAM Size | 128kB | |

| Maximum Supply Voltage | 3.6V | |

| Number of Programmable I/Os | 84 | |

| Minimum Operating Temperature | -40°C | |

| Maximum Power Dissipation Pd | 450W | |

| Maximum Operating Temperature | 85°C | |

| Height | 1.11mm | |

| Length | 10mm | |

| Standards/Approvals | REACH, RoHS3 | |

| Minimum Supply Voltage | 3V | |

| Instruction Set Architecture | RISC | |

| Automotive Standard | No | |

| Program Memory Type | FLASH | |

| 選取全部 | ||

|---|---|---|

品牌 XMOS | ||

Series XS1 | ||

Product Type Microcontroller | ||

Package Type QFN | ||

Mount Type Surface | ||

Pin Count 124 | ||

Device Core Multi-Core | ||

Interface Type JTAG, SPI | ||

Program Memory Size 128kB | ||

Maximum Clock Frequency 60MHz | ||

RAM Size 128kB | ||

Maximum Supply Voltage 3.6V | ||

Number of Programmable I/Os 84 | ||

Minimum Operating Temperature -40°C | ||

Maximum Power Dissipation Pd 450W | ||

Maximum Operating Temperature 85°C | ||

Height 1.11mm | ||

Length 10mm | ||

Standards/Approvals REACH, RoHS3 | ||

Minimum Supply Voltage 3V | ||

Instruction Set Architecture RISC | ||

Automotive Standard No | ||

Program Memory Type FLASH | ||

- COO (Country of Origin):

- SG

XS1 Event-Driven Processor

An XS1 combines a number of XCore™ processors, each with its own memory, on a single chip. The programmable processors are general purpose in the sense that they can execute languages such as C; they also have direct support for concurrent processing (multi-threading), communication and input-output. A high-performance switch supports communication between the processors, and inter-chip XMOS Links are provided so that systems can easily be constructed from multiple chips. The XS1 products are intended to make it practical to use software to perform many functions which would normally be done by hardware; an important example is interfacing and input-output controllers.

Each XCore processor provides the following resources:

32-bit processor providing up to 500MIPS

Eight hardware threads and 32 channel ends

Ten timers and six clock blocks

Four XMOS Links

64KBytes SRAM and 8KBytes OTP memory

The XCore is a multithreaded processing component with instruction set support for communication, input-output and timing. Thread execution is deterministic and the time taken to execute a sequence of instructions can be accurately predicted. This makes it possible for software executing on an XCore to perform many functions normally performed by hardware, especially DSP and I/O.,Each XCore thread has a dedicated set of registers and scheduling of threads is performed by hardware. Communication between threads is performed using hardware channels. Communication instructions transfer data directly between processor registers and channels, automatically scheduling and descheduling the communicating threads to control the flow of data.,The XCore has an efficient set of instructions to support conventional sequential programming languages. Its multithreading, communication and input-output instructions are designed to support modern concurrent programming languages. The instruction set is easily extensible to provide applications-specific instructions; these currently include support for long-arithmetic, CRC, DSP and cryptography.,Each XCore has a single unified memory system which is shared for program and data by all of the threads executed by the core. Multiple threads can share the same program in memory and can pass ownership of data between them. No caches are used.,The XCore has a tightly integrated set of I/O ports controlled directly by instructions. Data is transferred directly between processor registers and ports, avoiding the use of memory and minimizing latency. The ports can serialize and deserialize data enabling the processor to handle high speed data streams. They can also timestamp data arrival, and accurately control the time at which data is transferred to or from the pins.

相关链接

- XMOS Multi-Core 60 MHz 124-Pin QFN

- Microchip PIC 128kB FLASH, 28-Pin QFN

- Microchip PIC 128kB FLASH, 64-Pin QFN

- Microchip PIC18F27K40T-I/ML PIC 128kB FLASH, 28-Pin QFN

- Microchip PIC18F27K40-E/ML PIC 128kB FLASH, 28-Pin QFN

- Microchip PIC18LF27K40T-I/ML PIC 128kB FLASH, 28-Pin QFN

- Microchip PIC18F67K22-E/MR PIC 128kB FLASH, 64-Pin QFN

- Microchip AT90CAN128 Microcontroller 128kB FLASH, 64-Pin QFN